9장 - 페이징

4.5 페이징

- 프로세스를 일정크기(=페이징) 으로 잘라서 메모리에 넣음

- 프로세스는 페이지의 집합

- 메모리는 프레임의 집합

- 페이지를 프레임에 할당 ⇒ 페이지 = 프레임 크기는 같음

어떻게?

- MMU 내의 재배치 레지스터 값을 바꿈

- CPU 는 프로세스가 연속된 메모리 공간에 위치한다고 착각

- MMU 는 페이지 테이블이 됨

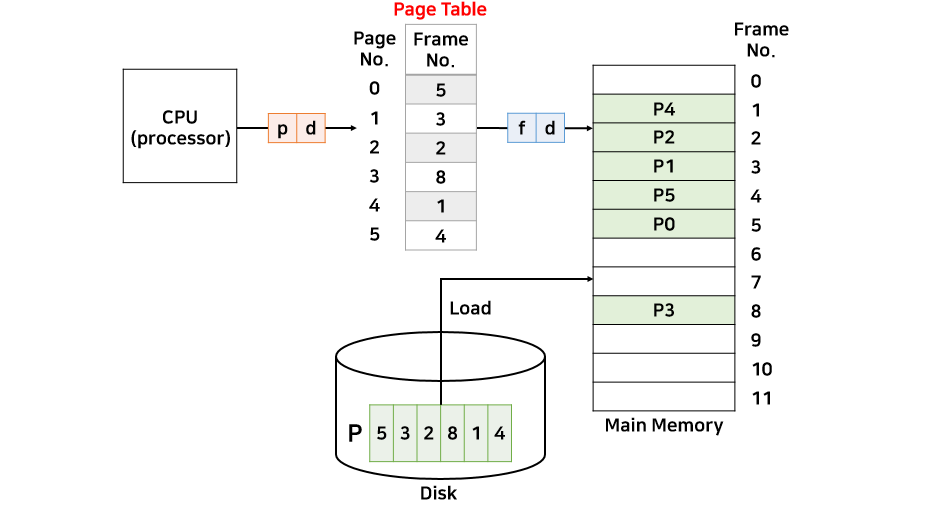

- Page size = 16bytes

- Page Table: 5, 3, 2, 8, 1, 4

- 예제: 50번지는 물리주소는?

d는 페이지 크기에 따라 달라지는데, 현재 페이지 크기는 16byte이다. 이는 **2^4이므로 d = 4** 이다.

p는 d를 제외한 나머지 크기이다.

그러면 실제로 p, d를 계산해보자. 현재 논리 주소는 50이며, 이진수로 나타내면 `110010`이다. 먼저 d는 4이므로 이 이진수의 뒤에서 4칸이 d이다. d를 제외한 나머지 2칸이 p가 된다.

p는 이진수로 11이고, 십진수로 3이다. 즉, 페이지 테이블의 페이지 번호 3번을 가리킨다. 페이지 3번에 해당하는 프레임 번호는 8번이므로, 물리주소를 구성하는 f값은 8이 된다.

논리주소

- CPU 가 내는 주소는 2진수로 표현, m 비트

- 하위 n 비트는 offset / displacement (변위)

- 상위 m-n 비트는 페이지 번호 (n=d, m-n=p)

주소변환

- 논리주소 → 물리주소

- 페이지 번호는 페이지 테이블 인덱스 값

- p 에 해당되는 테이블 내용이 프레임 번호임

- d 변위는 변하지 않음

페이지 테이블 만들기

- CPU 레지스터

- 장점: 속도가 빠름,

- 단점: 페이지 테이블 사이즈가 작음

- 메모리

- 장점: 페이지 테이블 사이즈가 큼

- 단점: 속도가 느림

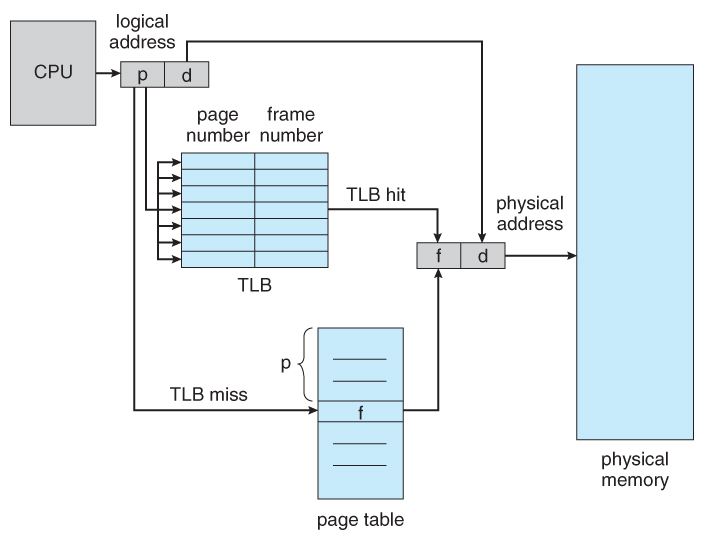

- TLB (Translation Look-aside Buffer)

- 일종의 page table 의 캐시라고 볼수 있음

- CPU → TLB 해당 주소 존재하는지 확인 → 존재하면 주소 변환(TLB Hit)/ 없으면 page_table 로 접근(TLB miss)

- 척도: 테이블 엔트리 개수 vs 변환 속도

- 유효메모리 접근시간: 메모리에서 데이어 읽어올때의 시간

- Tm(메모리 접근시간) = 100ns, Tb (TBL 탐색시간) = 20ns, hit ratio = 80%

- TLB 미스 = 220ns (20:탐색시간 + 100:페이지테이블접근시간 + 100: 메모리 접근시간)

- 0.8 * 120 + 0.2 * 220 = 40%

- 보호: 해킹 방지

- 모든 주소는 페이지 테이블 경유

- 페이지 테이블 엔트리마다 r,w,x 비트 두어서 페이지에 대한 접근 제어 가능

- 권한 밖의 명령이 들어오면 인터럽트 발생

- 공유: 메모리 낭비 방지

- 프로세스 구성 = code + data + stack

- 같은 프로그램을 쓰는 복수개의 프로세스가 있다면 code 는 공유 가능 ⇒ non-selfmodifying code = 실행되었을때 코드가 변경되지 않음

- 프로세스의 페이지 테이블 코드 영역이 같은 곳을 가리키도록함